# A-SSCC 2025 Review

KAIST 전기및전자공학부 석박사통합과정 이동윤

## Session 19 High-speed, High-resolution SAR and Pipelined ADCs

ADC 연구는 꾸준히 high speed, high resolution, low power를 동시에 달성하는 방향으로 진화해 왔다. 통신용 프론트엔드에서는 TI-SAR, pipelined-SAR, ring amplifier 기반, TDC-assisted, hybrid 구조 등이 고속·중고해상도 ADC의 주된 연구 축을 이루어 왔고, IoT·센서 인터페이스 영역에서는 NS-SAR, Incremental/Zoom ADC 등의 에너지 효율 중심 구조가 주로 연구되었다. 이와 병행해 CIS column ADC나 대규모 array 기반 구조, 그리고 cryo/edge/AI 가속기 등 특수 응용에 최적화된 비정형 ADC까지 등장하며, 응용 도메인 별로 요구 사양과 설계 철학이 세분화되는 추세다. ASSCC 2025 Session 19는 이 중에서도 특히 통신·무선 SoC를 겨냥한 고속 ADC와, 멀티모드·array 구조를 통한 시스템 레벨 효율 향상에 초점을 맞춘 논문들로 구성되어 있다.

### #19-3 TDC-assisted Pipelined-SAR ADC

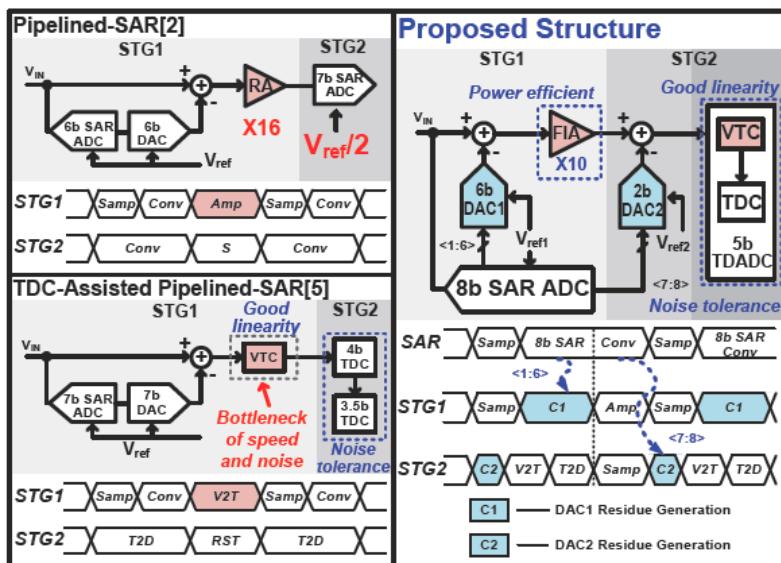

19.3 "A 3.4mW 64.5dB SNDR 800MS/s 12b Pipelined-SAR/TDC ADC with Parallel Amplification and Quantization"은 Pipelined-SAR에서 가장 까다로운 블록인 Residue Amplifier(RA)의 설계 부담을 줄이기 위해 등장한 TDC-assisted Pipelined-SAR 계열 구조가, 다시 VTC/TDC 쪽에서 speed·noise 병목을 맞는 상황을 정면으로 해소하는 논문이다. 기본 컨셉은 2-stage 구조에서 1단을 "SAR 기반 Coarse Quantizer + 단순 RA"로 두고, 2 단을 "VTC/TDC 기반 Fine Quantizer"로 두어 고속성과 RA 요건 완화를 동시에 얻는 것이다.

이 논문에서 제안하는 구조는 1st stage에 Auxiliary 8b SAR ADC를 두고, 그 코드 중 상위 6b는 메인 MDAC(CDAC1)에 feedback하여 coarse residue를 만들고, 하위 2b는 RA 이후의 작은 CDAC2 쪽으로 넘겨 2 LSB를 동시(Parallel)로 처리하는 것이 핵심이다. 이렇게 하면 SAR 8b를 전부 MDAC에 직접 쓰지 않고 6b만 앞단 MDAC1에 쓰기 때문에, MDAC의 스위칭 횟수와 비교 횟수에 따른 지연을 줄일 수 있고, 나머지 2b는 RA 증폭 구간과 병렬로 진행되므로 전체 conversion latency를 단축할 수 있다. Residue는 단순 Open-loop Floating Inverter Amplifier(FIA)로 약 10배 정도 증폭된 뒤, 작은 CDAC2를 겸한 VTC에 의해 시간 영역으로 변환되고, 5b TDC가 fine quantization을 담당해 최종적으로  $6+2+5-1$ (bit redundancy)=12b 출력을 만든다.

이 아키텍처에서 중요한 insight는 “TD ADC는 작은 입력 스윙에서 노이즈·선형성이 유리하다”는 점을 이용해, RA의 이득 요구와 선형성·잡음 요구를 크게 낮춘 것이다. 2nd stage가 SAR가 아니라 TDC이므로, 1st stage RA는 전통적인 고이득·저왜곡 ringamp 대신, 매우 단순한 open-loop FIA로 충분하고, 실제 설계에서도 전체 ADC 전력 3.4mW 중 약 11%만을 RA에 할당하면서 12b 급 정확도를 달성한다. 또한 VTC의 충전 커패시터를 메인 CDAC1과 분리해 작은 CDAC2(40fF)를 쓰도록 함으로써 V2T 변환 시간을 줄이고, 전체 변환 속도를 800MS/s까지 끌어올렸다. 결과적으로 이 구조는 28nm에서 단일 채널 12b, 800MS/s, 3.4mW, Walden FoM 4fJ/conv-step, Schreier FoM 173dB를 달성해 Wi-Fi 7(4K QAM, 최대 320MHz BW)의 베이스밴드 ADC 요구를 매우 효율적으로 만족시키는 구현 사례를 보여준다.

[그림 1] 본 연구에서 제시하는 TDC-assisted SAR 구조와 선행연구의 비교

#### #19-4 Heterogeneous Programmable Converter Array (H-PCA)

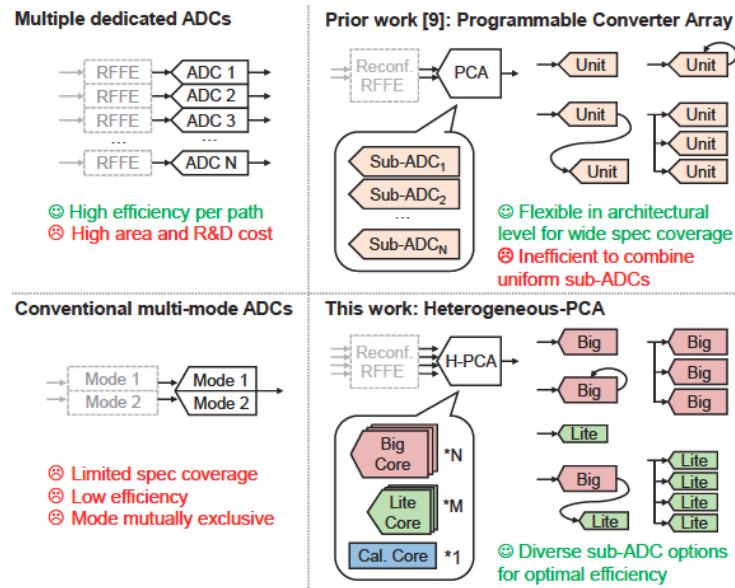

19.4 “A Heterogeneous Programmable A/D Converter Array Covering 2–500MHz BW and 81.4–58.7dB SNDR with over 170dB FoMs”는 최근 급증하는 multi-standard/multi-band 통신 규격을 하나의 SoC에서 동시에 지원해야 하는 요구에 대한 보다 시스템적인 해법을 제시한다. 기존 접근은 각 규격(예: GSM, LTE, NR, Wi-Fi)마다 전용 ADC를 두거나, 단일 고 성능 broadband ADC를 쓰는 방식이었는데, 전자는 실리콘 면적·개발비가 크고 후자는 소비전력이 과도하다는 문제가 있다. Multi-mode / reconfigurable ADC는 이 간극을 줄이는 방향으로 연구돼 왔으나, 대부분 모드 간 spec 범위가 제한적이거나, 효율이 떨어지거나, 동시에 여러 모드를 켜기 어렵다는 한계가 있었다.

이와 대조적으로 Programmable Converter Array(PCA)는 여러 개의 sub-ADC를 array로 배치하고 필요에 따라 직렬·병렬로 재구성하여 다양한 모드를 만들 수 있는 개념인데, 종래 PCA는 (1) 모든 sub-ADC를 균일하게 설계(Uniform partition)해 아키텍처별 최적화가 어렵고, (2) residue 전달이 전압 모드에 fully-connected 입력이라 기생 RC에 매우 민감해 확장성이 떨어지는 문제가 있었다. 19.4 논문은 이를 해결하기 위해, (1) 서로 다른 특성을 가진 이기종(Heterogeneous) Core를 섞어 쓰는 H-PCA 개념과, (2) group-connected input bus + low-Zin current-mode residue bus를 도입하여 확장성을 대폭 끌어올린 것이 핵심이다.

H-PCA는 세 가지 핵심 요소로 구성된다. 첫째, Big Core는 1.5pF CDAC와 GM-C 프리앰프를 갖춘 13b SAR로, NS-SAR, 고정밀 SAR, 또는 Pipe-SAR의 1단으로 동작하며, 큰 커패시터와 전치 증폭을 통해 70dB 이상의 SNR을 요구하는 모드를 커버한다. 둘째, Lite Core는 0.25pF CDAC를 사용하는 11b SAR로, 저전력 모드 또는 Pipe-SAR 후단 스테이지에 최적화되어 약 60dB SNR 수준에서 높은 에너지 효율을 목표로 설계되었다. Big/Lite 코어 모두 시간 인터리빙이 가능해, Big Core 3개를 TI로 묶어 200MHz BW, 66dB SNDR, Lite Core 4개를 TI로 묶어 500MHz BW, 약 59dB SNDR을 달성하는 등 다양한 모드를 구성할 수 있다. 셋째, Dither Core는 공용 보정 코어로, PRNG 기반 전압/전류 dither를 Big Core와 residue bus에 주입하여 각 TIA의 이득과 전체  $GM \times TIA$  gain을 순차적으로 추출하고, Core 간 gain error를 background로 정렬하는 데 사용된다.

이 구조를 시스템적으로 가능하게 만드는 열쇠는 저입력임피던스(Current-mode) residue bus이다. 종래 PCA에서는 residue를 전압 모드로 전달하거나, 비교적 높은  $Z_{in}$ (예:  $480\Omega$ )의 TIA를 이용한 전류 모드를 사용했기 때문에, 버스 배선에 깔리는 기생 C와 곱해지는 시상수(예:  $C_p=100fF$ 일 때 48ps)가 크고, Core 간 물리적 거리에 따라 속도·SNDR이 민감하게 변했다. 19.4에서는 gm-boosting과 Kelvin connection을 적용한 공통 게이트 기반 입력 구조로 TIA의  $Z_{in}$ 을 약  $40\Omega$ 까지 낮춰, 동일  $C_p$ 에서 시간 상수를 4ps 수준으로 줄였다. 그 결과 residue bus 상의 추가 RC가 사실상 무시 가능해져, Big/Lite Core 사이의 거리( $50\sim420\mu m$ )가 달라져도 Pipe-SAR 모드 SNDR이 거의 일정함을 실측으로 보인다. 이는 “Core를 칩 위에 자유롭게 배치하고 여러 조합으로 연결해도 성능이 깨지지 않는” PCA의 확장성을 처음으로 설득력 있게 입증한 결과다.

프로토타입 H-PCA는 28nm CMOS에서 3개의 Big Core와 4개의 Lite Core로 구성되어, NS-SAR(2MHz BW, 81.4dB SNDR), Big-core SAR(10MHz, 70dB), Lite-core SAR(133MHz, 60dB), Pipe-SAR(100MHz, 71dB), Noise-shaped Pipe-SAR(50MHz, 76dB), 3×TI Big-SAR(200MHz, 66dB), 4×TI Lite-SAR(500MHz, 58.7dB) 등 총 7개 대표 모드를 하나의 IP로 구현한다. 모

든 모드에서 Schreier FoM 170dB 이상, 최대 176.5dB(100MHz BW)까지 달성하며, 동일한 규격 범위를 개별 single-mode ADC들로 커버하는 경우 대비 활성 면적을 약 56% 절감하는 것으로 보고된다. 또한 IQ 채널 4개를 동시에 처리하는 Wi-Fi/NR 시나리오에서 4 concurrent mode 동작을 시연해, “실제 단말 SoC에서 하나의 Reconfigurable ADC IP로 전 대역·전 표준을 커버한다”는 PCA 비전이 실현 가능한 수준에 도달했음을 보여준다.

[그림 2] 본 연구에서 제시하는 H-PCA 구조와 선행연구의 비교

## 저자정보

### 이동윤 석박사통합과정 대학원생

- 소속 : KAIST

- 연구분야 : Body-Channel-Communication Transceiver

Design for Body-Area Network in Biomedical Application

- 이메일 : [dongyoon.lee@kaist.ac.kr](mailto:dongyoon.lee@kaist.ac.kr)

- 홈페이지 : <https://impact.kaist.ac.kr>

# A-SSCC 2025 Review

단국대학교 파운드리공학과 석사과정 장준서

## Session 9: High Precision ADCs

Session 9에서는 총 4편의 High Precision ADC 논문이 발표되었다. 본 세션의 논문들은 공통적으로 저주파 대역에서의 높은 정확도와 선형성, 그리고 공급 전압 및 공정 변화에 대한 안정성을 어떻게 확보할 것인가에 초점을 맞추고 있다. 특히 Incremental  $\Delta\Sigma$  ADC, SAR ADC, 그리고 이들의 하이브리드 구조를 활용하여 정확도와 대역폭 간의 트레이드오프를 완화하려는 접근이 두드러졌다. 특히 기존 구조의 한계를 구조적으로 극복하려는 시도가 두드러졌으며, 본 리뷰에서는 이러한 흐름을 잘 대표한다고 판단되는 두 편의 논문을 선정하였다.

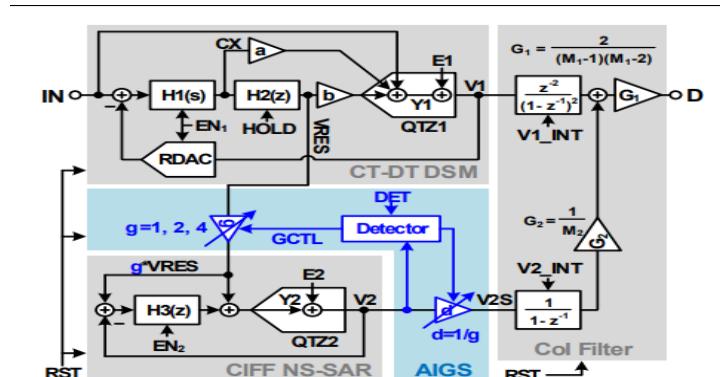

**#9-1** KAIST에서 발표한 논문으로, Incremental  $\Delta\Sigma$  ADC와 MASH 구조를 결합한 Two-Step 하이브리드 ADC를 제안한다. Incremental  $\Delta\Sigma$  ADC의 높은 DC 정확도를 유지하면서도 대역폭 확장 시 성능 저하가 발생하는 문제를 해결하기 위해, 스테이지 간 이득을 자동으로 조절하는 Automatic Inter-Stage Gain Selection(AIGS) 기법을 도입하였다. 측정 결과, 제안된 ADC는 160 kHz 대역폭에서 약 97 dB 수준의 SNDR과 100 dB 이상의 DR을 달성하였으며, AIGS 적용 시 고정 이득 설정 대비 성능이 유의미하게 향상됨을 확인하였다. 또한 변환 단계 일부를 비활성화하는 방식으로 전력 소모를 줄이면서도, 공급 전압 변화에 따른 성능 변동이 작아 안정적인 동작 특성을 보였다. 이러한 결과는 Incremental  $\Delta\Sigma$  ADC가 하이브리드 구조와 적응형 이득 제어를 통해 정밀 계측 응용에서 정확도와 대역폭을 동시에 확장할 수 있음을 보여준다.

[그림 1] AIGS를 적용한 Incremental Two-Step 하이브리드 DSM+CIFF NS-SAR ADC 구조

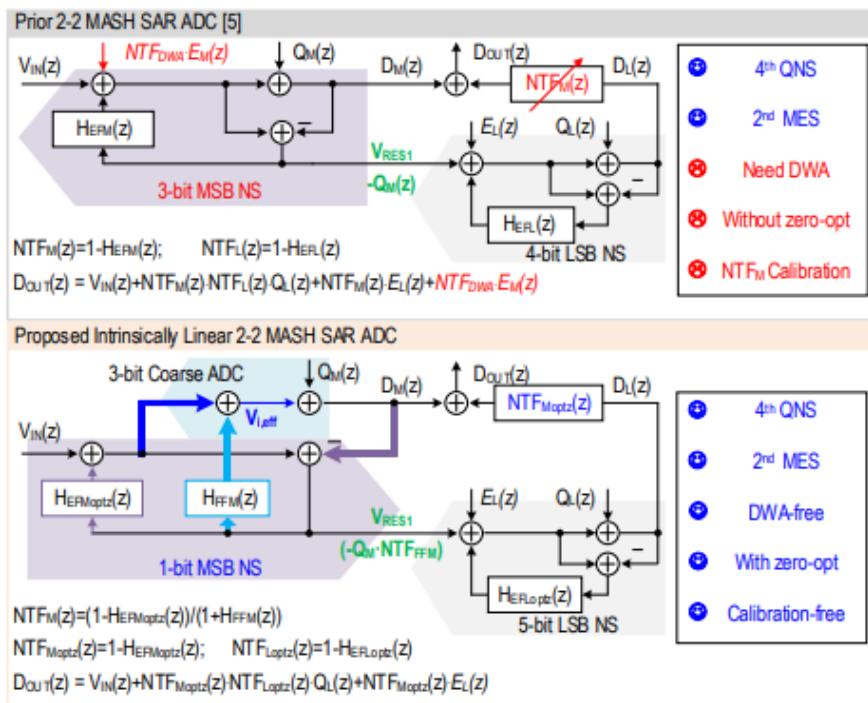

#9-3 Xidian University에서 발표한 논문으로, 구조적 기법을 통해 높은 선형성을 확보한 MASH SAR ADC를 제안한다. 기존 MASH SAR ADC는 높은 해상도를 제공할 수 있으나, 아날로그 증폭기 비선형성과 잔여 전하 누적에 의해 SFDR 확보에 한계가 존재하며, 이를 보완하기 위해 DWA나 디지털 캘리브레이션에 의존하는 경우가 많았다. 본 논문에서는 MSA(Multi-Step Amplification) Enhancement와 Incremental Correlated Level Shifting 기법을 적용하여, 별도의 DWA나 디지털 캘리브레이션 없이도 높은 선형성을 구조적으로 확보하였다. 측정 결과, 제안된 ADC는 100 kHz 대역폭에서 105 dB 이상의 SFDR를 달성 하였으며, 입력 주파수 전반에 걸쳐 약 89 dB 수준의 SNDR를 유지하였다.

특히 고주파 입력 조건에서도 SFDR 열화가 제한적으로 나타나, 구조적 선형성 확보의 효과가 실증으로 확인되었다. 추가적으로, 제안된 구조는 MASH SAR ADC에서 문제가 되기 쉬운 잔여 전하(residue) 누적과 증폭 단계 비선형성을 MSA 기반 다단 증폭과 correlated level shifting을 통해 효과적으로 억제하였다. 이로 인해 입력 주파수 변화에 따른 선형성 저하가 비교적 완만하게 나타났으며, 고해상도 MASH SAR ADC에서 흔히 요구되는 복잡한 보정 회로를 배제하고도 정밀 센서 인터페이스에 적합한 성능을 확보할 수 있음을 보여준다.

[그림 2] 기존 MASH SAR ADC와 제안된 구조적 선형 MASH SAR ADC의 비교

## Session 23: High Precision ADCs

Session 23에서는 총 5편의 High Performance ADC 논문이 발표되었으며, 고속 동작 환경에서 대역폭, 변환 속도, 전력 효율, 그리고 공정·온도·전압 변화에 대한 강건성을 동시에 확보하려는 연구들이 주를 이루었다. Pipeline SAR, Noise-Shaping SAR, 그리고 CIS용 Column-Parallel ADC 등 응용 지향적인 구조가 다수 제시되었다. 본 리뷰에서는 이 중에서도 고속 ADC에 고차 Noise-Shaping을 안정적으로 적용한 구조, 실제 시스템 레벨에서 고속, 고선형 동작을 검증한 사례라는 관점에서, 두 편의 논문을 선정하였다.

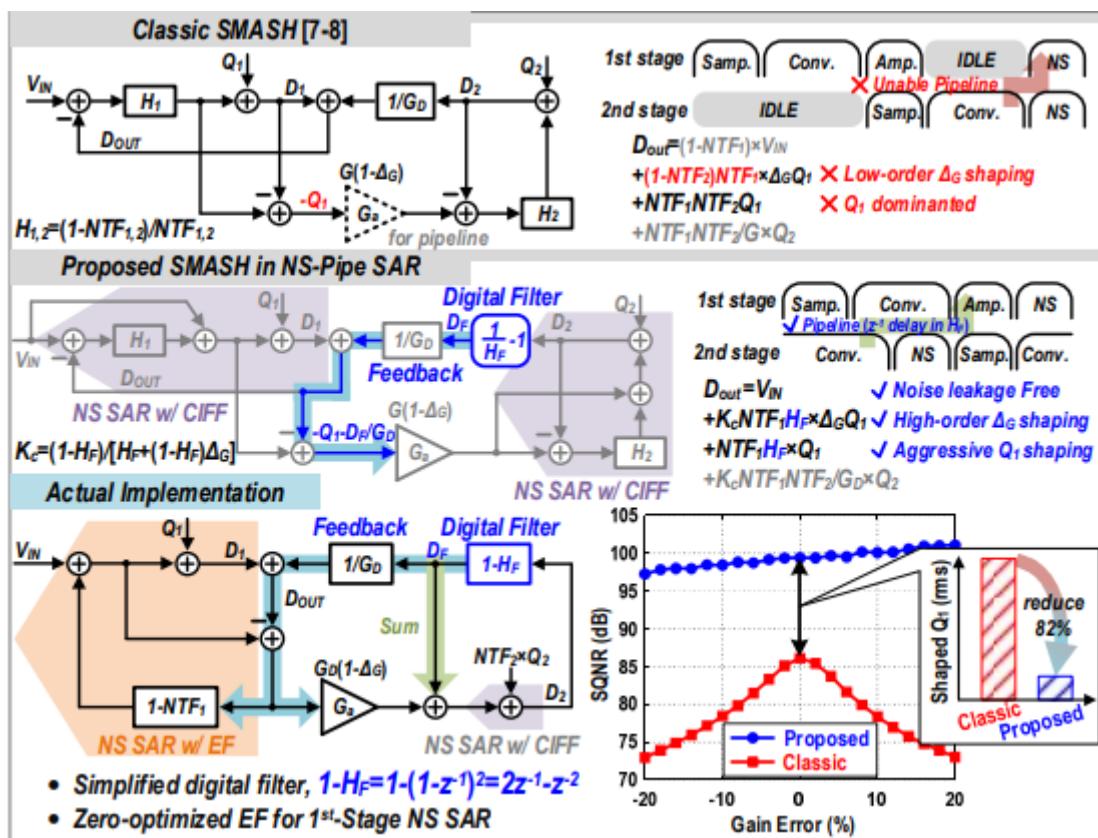

**#23-1** University of Macau에서 발표한 논문으로, Pipeline SAR ADC에 4차 Noise-Shaping을 적용한 고속 ADC 구조를 제안한다. 고속 동작 환경에서 고차 Noise-Shaping 적용 시 발생할 수 있는 루프 안정성 및 스테이지 간 이득 오차 문제를 구조적으로 해결하는 것이 본 논문의 핵심이다. 측정 결과, 제안된 ADC는 15 MHz 대역폭에서 약 80 dB 수준의 SNDR를 달성하였으며, 출력 스펙트럼을 통해 명확한 4차 Noise-Shaping 특성이 확인되었다. 또한 온도 및 공급 전압 변화에 따른 성능 변동이 제한되어, 고속 ADC에서 요구되는 PVT 강건성을 확보하였다. 이는 Pipeline SAR 구조에서도 고차 Noise-Shaping이 실용적으로 적용될 수 있음을 보여준다.

[그림 3] 기존 SMASH 구조와 제안된 NS-Pipeline SAR용 SMASH 구조의 신호 흐름 및 실제 구현

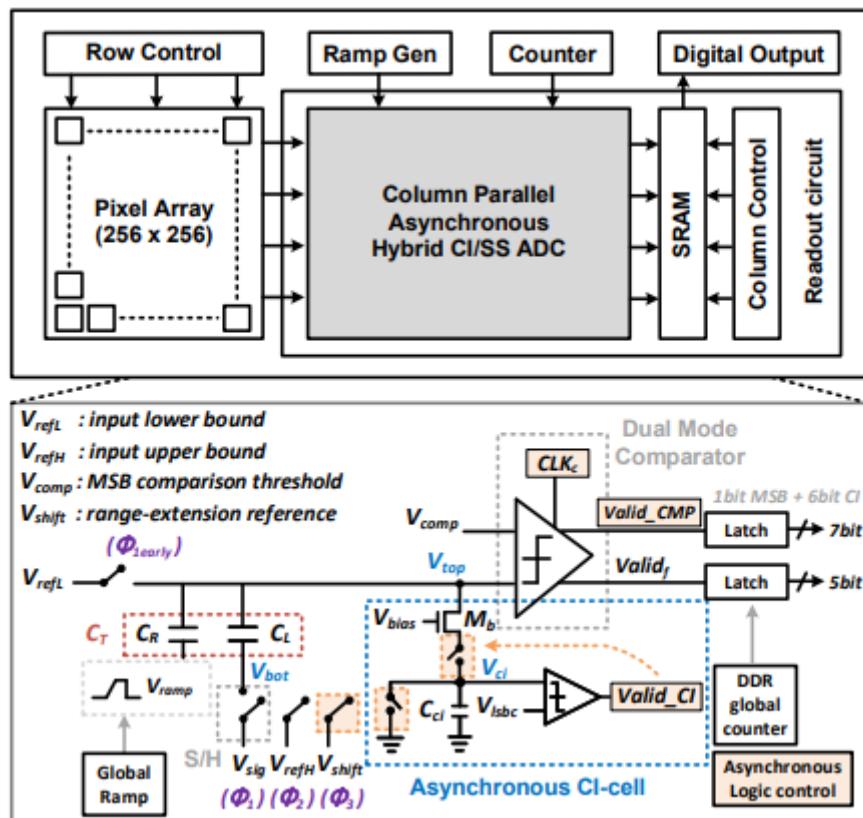

#23-5 National Tsing Hua University에서 발표한 논문으로, Column-Parallel Hybrid CI/SS ADC를 집적한  $256 \times 256$  CMOS Image Sensor(CIS)를 제안한다. Column-parallel ADC에서 요구되는 고속 변환 성능과 컬럼 간 균일성을 동시에 확보하는 것이 본 논문의 주요 목표이다. 제안된 구조는 비동기(Asynchronous) Charge-Injection(CI) 아키텍처와 Hybrid Quantization(CI/Single-Slope) 방식을 결합하여, 고속 동작 시에도 비교기 및 디지털 제어에 따른 지연과 비선형성을 최소화하였다. 또한 Dark Frame Calibration을 통해 컬럼 고정 패턴 잡음(FPN)을 효과적으로 제거하였다. 측정 결과, 제안된 ADC 어레이에는 435kS/s 변환 속도에서 약 9.6-bit 수준의 ENOB를 달성하였으며, 컬럼 간 비균일성은 입력 범위 전반에서 1.2 LSB 이내로 제한되었다. 실제 이미지 캡처 결과에서도 컬럼 고정 패턴 잡음이 효과적으로 제거됨을 확인하였으며, 이는 대규모 병렬 ADC 어레이에서도 안정적인 동작이 가능함을 보여준다. 이러한 결과는 제안된 비동기 CI 기반 Hybrid 구조가 고속·고 해상도 CIS 응용에 적합한 설계 방향임을 실증한다.

[그림 4] CIS 프로토타입 구조와 제안된 컬럼 병렬 하이브리드 CI/SS ADC

## 저자정보

### 장준서 석사과정 대학원생

- 소속 : 단국대학교

- 연구분야 : Analog front end 설계

- 이메일 : cah7781@naver.com

- 홈페이지 : <https://sites.google.com/dankook.ac.kr/acs-lab/home>